Abstract

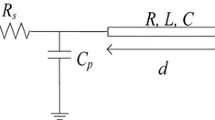

The limiting factor for high-performance systems is being set by interconnection delay rather than transistor switching speed. The advances in circuits speed and density are placing increasing demands on the performance of interconnections, for example chip-to-chip interconnection on multichip modules. To address this extremely important and timely research area, we analyze in this paper the circuit property of a generic distributedRLC tree which models interconnections in high-speed IC chips. The presented result can be used to calculate the waveform and delay in anRLC tree. The result on theRLC tree is then extended to the case of a tree consisting of transmission lines. Based on an analytical approach a two-pole circuit approximation is presented to provide a closed form solution. The approximation reveals the relationship between circuit performance and the design parameters which is essential to IC layout designs. A simplified formula is derived to evaluate the performance of VLSI layout.

Similar content being viewed by others

References

T.C. Edwards,Foundations for Microstrip Circuit Design, Wiley: New York, 1984.

B.J. Rubin, “An Electromagnetic Approach for Modeling High-Performance Computer Package,”IBM J. Res. Dev., Vol. 34, pp. 585–599, 1990.

L.V. Blake.Transmission Lines and Waveguides, Wiley: New York, 1969.

D. Zhou, F.P. Preparata, and S.M. Kang, “Interconnection Delay in Very High-Speed VLSI,”IEEE Trans. Circuits Systems, Vol. 38, pp. 779–790, 1991.

L.W. Nagel, “Spice2, A Computer Program to Simulate Semiconductor Circuits,”Tech. Rep. ERL-M520, Univ. Calif. at Berkeley, 1975.

D.S. Gao, A.T. Yang, and S.M. Kang, “Modeling and Simulation of Interconnection Delays and Crosstalks in High-Speed Integrated Circuits,”IEEE Trans. Circuits Systems, Vol. 37, pp. 1–10, 1990.

W.M. Dai, “Performance Driven Layout of Thin-Film Substrates for Multichip Modules,” inProc. ISCAS'91, Vol. 4, pp. 2308–2311, 1991.

H.B. Bakoglu,Circuits, Interconnections and Packaging for VLSI, Addison-Wesley, pp. 81-133, 1990.

D. Zhou, F. Tsui, D.S. Gao, and J.S. Cong, “A Distributed-RLC Model for MCM Layout,”Proc. IEEE Multichip Model Conf. pp. 191-197, 1993.

D. Zhou, F. Tsui, and D.S. Gao, “High Performance Multichip Interconnection Design,”Proc. 4th ACM/SIGDA VLSI Physical Design Workshop, pp. 32-43, 1993.

K.D. Boses, A.B. Kahng, M.A. McCoy, and G. Robins, “Toward Optimal Routing Trees,”Proc. 4th ACM/SIGDA VLSI Physical Design Workshop, pp. 44-51, 1993.

L.T. Pillage and R.A. Rohrer, “Asymptotic Waveform Evaluation for Timing Analysis,”IEEE Trans. CAD, Vol. 9, pp. 352–366, 1990.

J. Rubinstein, P. Penfield, and N.A. Horowitz, “Signal Delay in rc Tree Networks,”IEEE Trans. CAD, Vol. CAD-2, No. 3, pp. 202–211, 1983.

J.S. Cong, K.S. Leung, and D. Zhou, “Performance-Driven Interconnect Design Based on Distributed-RC Delay Model,”Proc. 30th ACM/IEEE Design Automation Conf., 1993.

J. Cong, A. Kahng, G. Robins, M. Sarrafzadeh, and C.K. Wang, “Probably Good Performance-Driven Global Routing,IEEE Trans. Computer-Aided Design, Vol. 11, No. 6, pp. 739–752, 1992.

K.D. Boses, J. Cong, K.S. Leung, and D. Zhou, “On High-Speed VLSI Interconnects: Analysis and Design,”IEEE Asia-Pacific Conf. Circuits and Systems, 1993.

Author information

Authors and Affiliations

Additional information

1. Notice that s k is the solution of equation (7).

2. The case of an arbitrary driving functionf(t) can be discussed similarly.

3. When context is clear we will omit the subscript ofγ.

4. This assumption can be satisfied in most practical interconnection design problems.

5. We suppose thatγ keeps the value determined from the single line case.

6. Recall that we have assumed that a step input is applied at the root of the tree.

Rights and permissions

About this article

Cite this article

Zhou, D., Su, S., Tsui, F. et al. A simplified synthesis of transmission lines with a tree structure. Analog Integr Circ Sig Process 5, 19–30 (1994). https://doi.org/10.1007/BF01673903

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF01673903